# Design and Implementation of Five Stages Pipelined RISC Processor on FPGA

Dania Alamen (022160629) Amani BenYousuf (022150310)

A report submitted in part fulfilment of the degree of

### **Bachelor in Computer Engineering**

Supervisor: Dr. Mohamed Eljhani

Department of Computer Engineering University of Tripoli

November 15, 2024

# Declaration

This Pipelined Processor project report has been prepared on the basis of our own work for the award of the degree of Bachelor in Computer Engineering under the guidance of Dr. Mohamed Eljhani.

Word Count: approximately 15,000 words

Student Names:

Date of Submission:

Signature:

# Acknowledgement

I would like to thank my project supervisor, Dr. Mohamed Eljhani for providing nice ideas to work upon and to his valuable guidance and support for doing this project. I sincerely want to thank my Dr. for his time to review my project report and their suggestion

## Abstract

The main purpose of this project is to design, verify and implement a 5 stages pipelined processor that used as embedded system, which is a subset of a 16-bit RISC (Reduced Instruction Set Computer) CPU (Central Processing Unit) architecture. The basic modules of this processor are programmed and simulated using Verilog HDL (Hardware Description Language), and implemented on Cyclone IV FPGA (Field-Programmable Gate Arrays) board.

The Processor used as an embedded system in many applications like mobile computing, automobiles, industrial process controls, home appliances, office automation, and security etc, can be done by using processing element. Two commonly used processor architectures are CISC (Complex Instruction Set Computer) and RISC processor. The RISC processor uses large number of simple instructions and performs complex operations by using pipeline concept with improved performance.

# Content

| Acknowled  | lgement                          | 3  |

|------------|----------------------------------|----|

| Abstract   |                                  | 4  |

| Chapter 1: | Introduction                     | 9  |

| 1.1        | Requirements                     | 10 |

| 1.2        | ModelSim HDL Simulator           | 11 |

| 1.3        | Altera Quartus II                | 11 |

| 1.4        | Verilog HDL Language             | 12 |

| 1.5        | DE2i-150 FPGA Board              | 13 |

| Chapter 2: | Design Methodology 1             | 5  |

| 2.1        | Datapath                         | 16 |

| 2.2        | The Instruction Set Architecture | 17 |

| 2.3        | Five-stage pipeline              | 20 |

| 2.4        | Memory                           | 26 |

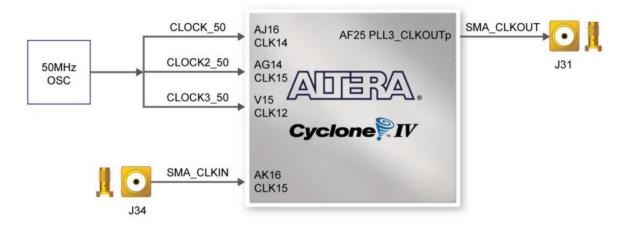

| 2.5        | Clock Generator                  | 29 |

| 2.6        | Processor controller             | 29 |

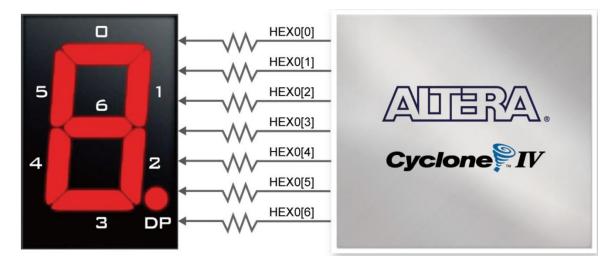

| 2.7        | Seven-Segment Interface          | 30 |

| Chapter 3: | Hazards Conflict                 | 31 |

| 3.1        | Structural hazard                | 31 |

| 3.2        | Data hazard                      | 31 |

| 3.3        | Control hazard                   | 33 |

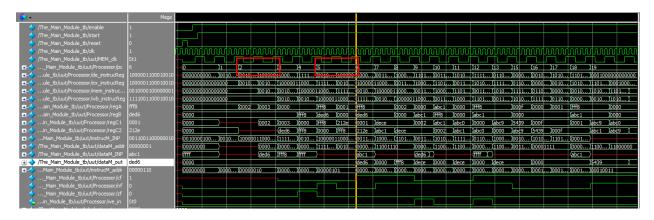

| Chapter 4: | Simulation Result                | 34 |

| 4.1        | Software simulation              | 34 |

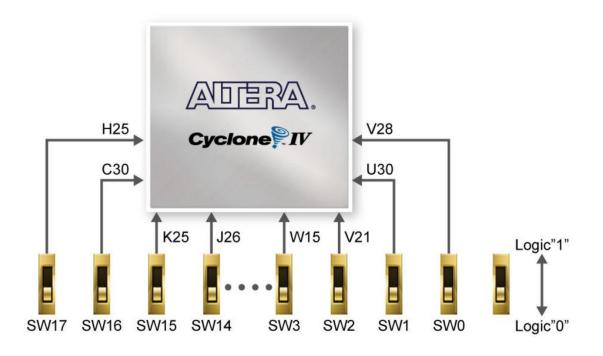

| 4.2        | Board-level verification         | 36 |

| Chapter 5: | Conclusion & Future Work4        | 1  |

| Reference  | s4                               | 2  |

| Appendix   | 4                                | 3  |

# **List of Figures**

| Figure 1. Appearance of CPU                                                      | 9  |

|----------------------------------------------------------------------------------|----|

| Figure 2. ModelSim Simulator                                                     | 11 |

| Figure 3. The main Altera Quartus II display                                     | 12 |

| Figure 4. The DE2i-150 board (top view)                                          | 14 |

| Figure 5. Basic Design Methodology                                               | 14 |

| Figure 6. Single-Cycle CPU logic architecture                                    | 15 |

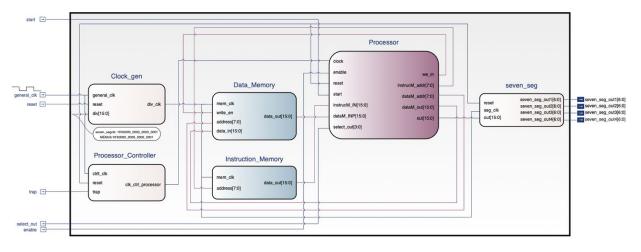

| Figure 7. CPU top view                                                           | 16 |

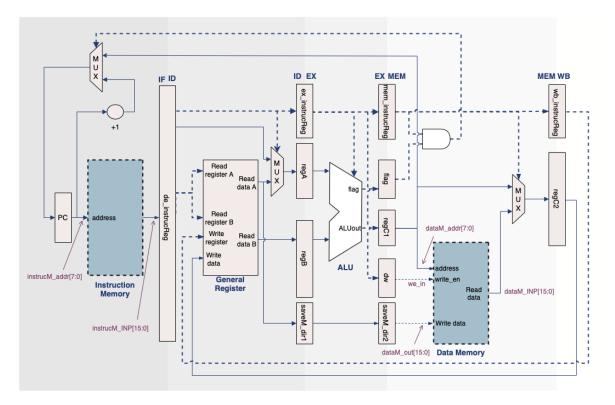

| Figure 8. CPU block-level circuit diagram                                        | 20 |

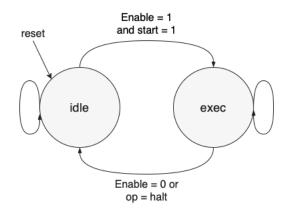

| Figure 9. CPU control state diagram                                              | 21 |

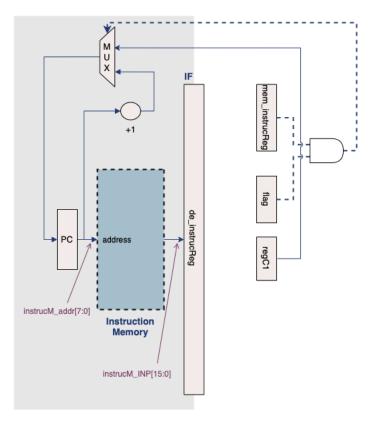

| Figure 10. IF stage                                                              | 21 |

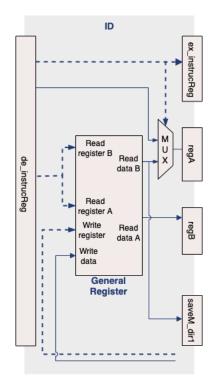

| Figure 11. ID stage                                                              | 22 |

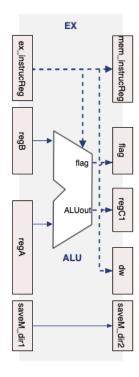

| Figure 12. EX stage                                                              | 23 |

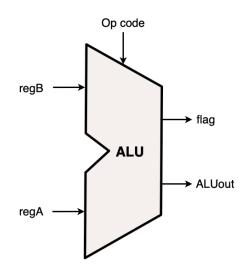

| Figure 13. ALU interface                                                         | 24 |

| Figure 14. MEM stage                                                             | 25 |

| Figure 15. WB stage                                                              | 26 |

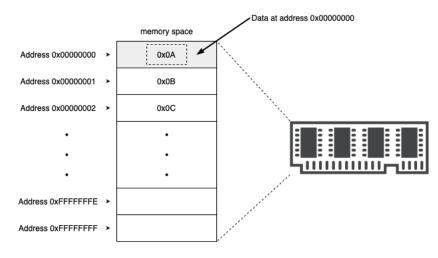

| Figure 16. Memory and Address                                                    | 26 |

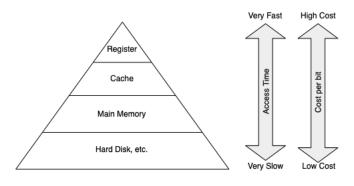

| Figure 17. Memory hierarchy                                                      | 27 |

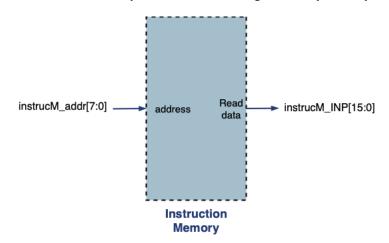

| Figure 18. Instruction Memory interface                                          | 28 |

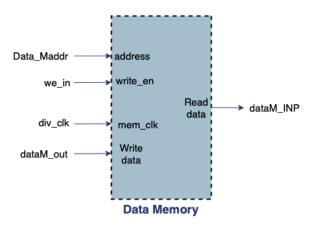

| Figure 19. Data Memory interface                                                 | 28 |

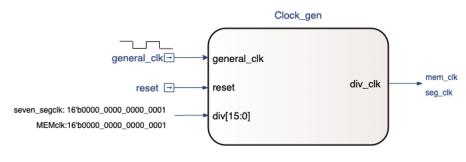

| Figure 20. Clock Generation                                                      | 29 |

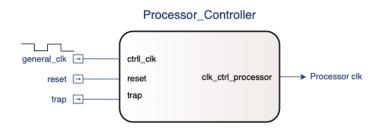

| Figure 21. Processor controller                                                  | 29 |

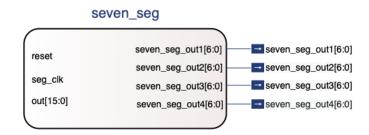

| Figure 22. Seven Segment Interface                                               | 30 |

| Figure 23. Connections between the 7-segment display HEX0 and Cyclone IV GX FPGA | 30 |

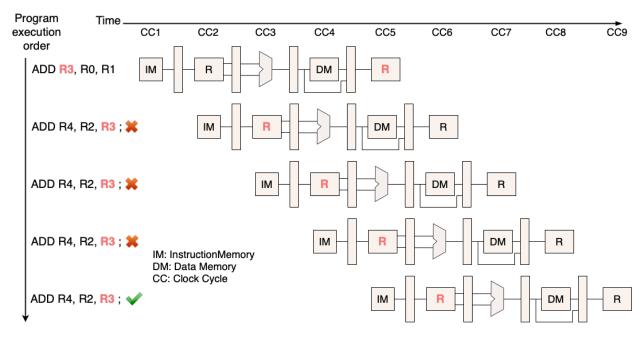

| Figure 24. Data Hazard                                                           | 31 |

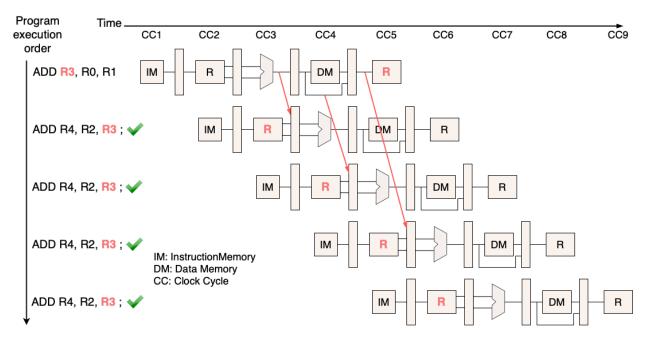

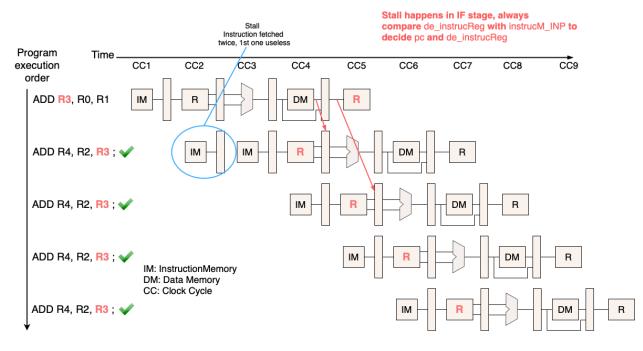

| Figure 25. Data Forwarding                                                       | 32 |

| Figure 26. LOAD Hazard Delay Mechanism                                           | 32 |

# **List of Tables**

| Table 1. Comparison of RISC and CISC     | 9  |

|------------------------------------------|----|

| Table 2. The Instruction set Format      | 18 |

| Table 3. 16-bit Instruction set encoding | 18 |

# **List of Abbreviations**

| Abbreviation | Definition                       |

|--------------|----------------------------------|

| RISC         | Reduced Instruction Set Computer |

| CPU          | Central Processing Unit          |

| HDL          | Hardware Description Language    |

| FPGA         | Field-Programmable Gate Arrays   |

| CISC         | Complex Instruction Set Computer |

| SPARC        | Scalable Processor Architecture  |

| MIPS         | Million Instructions Per Second  |

| ARM          | Advanced RISC Machine            |

| DEC          | Department Equipment Corporation |

| PDP          | Programmed Data Processor        |

| ISA          | Instruction Set Architectures    |

| TTL          | Transistor-Transistor Logic      |

| OPCODE       | Operation Code                   |

| PC           | Program Counter                  |

| IF           | Instruction Fetch                |

| ID           | Instruction Decode               |

## Chapter 1: Introduction

Among all kinds of CPUs in use, the RISC CPU has the majority market share. It is most commonly used in embedded systems, which are in almost every consumer product on the market. RISC CPUs are basic and offer low-power consumption and small size. They are sometimes referred to as load-store processor because of the basic mechanics upon which it operates. The idea of the RISC CPU is to reduce the complexity of the system and increase the speed. Any complex operation can be split into smaller chunks that can be calculated simultaneously in most cases. Other important features of the RISC CPU include uniform instruction coding, which allows faster coding. A good example is that the opcode (operation code) is always in the same bit position in each instruction, which is always one word long. Another advantage is a homogeneous register set, which allows any register to be used in any context and simplifies compiler design. Lastly, complex addressing modes are replaced by sequences of simple arithmetic instructions. The convenience of the RISC processor is a direct explanation for why it dominates the CPU market.

Figure 1. Appearance of CPU

According to the characteristics of the executed instructions, the CPU is divided into RISC and CISC two. Table 1 compares the characteristics of RISC and CISC, and gives their representative products.

| Table 1. | Comparison | of RISC | and Cl | ISC |

|----------|------------|---------|--------|-----|

|----------|------------|---------|--------|-----|

|      | Command<br>function | Number of instructions | hardware | high speed   | # of instructions performing<br>same processing | Representative products                               |

|------|---------------------|------------------------|----------|--------------|-------------------------------------------------|-------------------------------------------------------|

| RISC | simple              | Few                    | Simple   | Suitable for | many                                            | IBM Power, Sun MicroSystems<br>SPARC, MIPS, ARM, etc. |

| CISC | complex             | many                   | complex  | Not suitable | few                                             | Intel i386, 1BM System/360,<br>DEC PDP, etc.          |

The instruction function of the RISC class CPU is simple and there are few types. Correspondingly, the instruction functions of CISC class CPUs are complex. The advantage of RISC instruction simplification is that the internal structure of the CPU can be simplified, which is suitable for high-speed operation. But when doing the same operation, since each instruction is functionally simple, it needs to use

more instruction count than CISC. Although the internal structure of CISC is complex and not suitable for high-speed operation, the number of instructions for the same processing is less than that of RISC.

The biggest feature of the RISC architecture is that it only uses load and store instructions to access memory. This architecture is called Load/Store Architecture. The advantage of this is that the instruction set and pipeline design can be simplified. In this architecture, operation instructions can only operate on the data in the register.

MIPS stands for (Million Instructions Per Second) is a family of RISC ISA (Instruction Set Architectures). The MIPS processor, designed in 1984 by researchers at Stanford University, is a RISC processor. Compared with their CISC counterparts (such as the Intel Pentium processors), RISC processors typically support fewer and much simpler instructions.

The premise is, however, that a RISC processor can be made much faster than a CISC processor because of its simpler design. These days, it is generally accepted that RISC processors are more efficient than CISC processors; and even the only popular CISC processor that is still around (Intel Pentium) internally translates the CISC instructions into RISC instructions before they are executed.

RISC processors typically have "load-store architecture". This means there are two instructions for accessing memory: A load instruction to load data from memory and a store instruction to write data to memory. It also means that none of the other instructions can access memory directly.

The instruction pipelining is a technique that is used to execute multiple instructions. The advantage of this technique is that it allows a faster throughput. In pipelining, the instruction execution is usually divided into stages. The number of stages varies depending on implementation. In our case, we have a five-stage pipelined structure. The instruction is split into five different steps which can be executed in parallel and the instructions can be processed concurrently, i.e., starting one instruction before finishing the previous one.

The main aim of the project is to design a 16-bit pipelined processor. Verilog HDL is used as the hardware description language for writing the modules. The length of instruction and registers is 8 bits long. The modules are simulated and the final results of the simulation are analyzed. The designed processor runs fixed point integer arithmetic and logical instructions, branch instructions, and integer load/store instructions.

## 1.1 Requirements

Apart from developing only a conceptual model, we propose implementing our design practically to develop a prototype. Following this, we state the following requirements for a successful project implementation:

#### • Software Requirements:

- ModelSim HDL Simulator

- Quartus II

- Language Proficiency:

- Verilog

- Hardware environment:

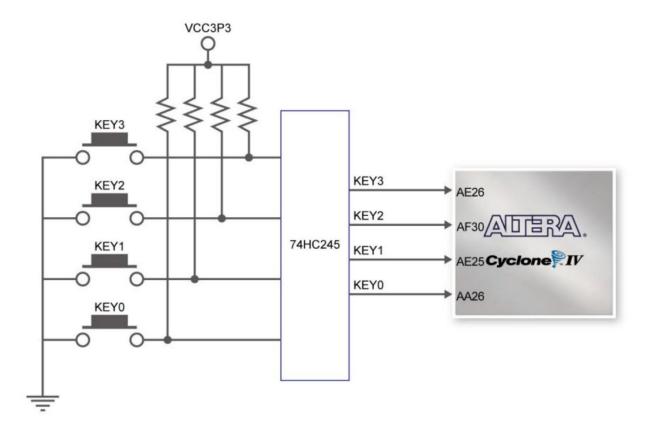

• DE2i-150 FPGA Development Board module (Cyclone IV EP4CGX150DF31) device

## 1.2 ModelSim HDL Simulator

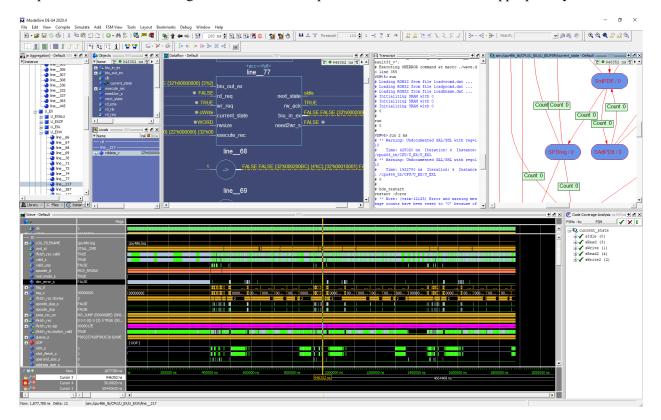

Modelsim is a program created by Mentor Graphics used for simulating behavioral, RTL, and gatelevel code, including VHDL and Verilog gate libraries, with timing provided by the standard delay format (SDF). It is the most widely use simulation program in business and education.

Simulation is a critical step in designing FPGAs and ASICs. Simulation allows the designer to stimulate his or her design and see how the code that they wrote reacts to the stimulus. A great simulation will exercise all possible states of the design to ensure that all input scenarios will be handled appropriately.

Figure 2. ModelSim Simulator

### 1.3 Altera Quartus II

Altera Quartus is programmable logic device design software produced by Altera Quartus enables analysis and synthesis of HDL designs, which enables the developer to compile their designs, perform timing analysis, examine RTL diagrams, simulate a design's reaction to different stimuli, and configure the target device with the programmer. Quartus includes an implementation of VHDL and Verilog for hardware description, visual editing of logic circuits, and vector waveform simulation.

| 💱 Quartus II 64-Bit - C:/dev/openSAFETY_DEMO/blackchannel/POWERLINK/fpga/boards/altera/terasic-de2-115/cn-pcp-s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | pi/ink                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| File Edit View Project Assignments Processing Tools Window Help 🗟                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | earch altera.com                      |

| 🗄 🗋 📸 💭 🖇 🛍 🛍 🖉 🥲 🚺 İnk-de2-115 💿 🗸 🏹 🐓 🏈 💿 🕨 🗞                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 🎙 🖄 🛈 👯 👯 🔹                           |

| Project Navigator 🛛 🕂 🗗 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |

| Entity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |

| Cydone IV E: EP4CE115F29C7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |

| ▷ 👷 toplevel 🚈                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |

| A Hierarchy I Files → Design Units ▲ ↓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |

| Tasks Tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | @                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |

| V Compile Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Version 13                            |

| V Analysis & Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | /iew New Quartus II<br>Information    |

| Edit Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Documentation                         |

| Tiew Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Notification Center                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |

| R A Contraction of the second |                                       |

| I Type ID Message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |

| Service / Processing /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |

| System / Processing /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | , , , , , , , , , , , , , , , , , , , |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0% 00:00:00                           |

Figure 3. The main Altera Quartus II display

### 1.4 Verilog HDL Language

Verilog HDL is one of the most popular HDL languages developed by Gateway Design Automation as a proprietary language for logic simulation in 1984. The language became an IEEE standard in 1995 (IEEE STD 1364) and was updated in 2001 and 2005.

Verilog HDL language is a case-sensitive language. Used for describing a digital system like a network switch or a microprocessor or a memory or a flip-flop. It means, that by using an HDL we can describe any digital hardware at any level. Designs, which are described in HDL are independent of technology, very easy for designing and debugging, and are normally more useful than schematics, particularly for large circuits.

Verilog HDL is commonly used to write text models that describe a logic circuit. Such a model is processed by a synthesis program, only if it is part of the logic design using simulation models to represent the logic circuits that interface to the design. This collection of simulation models is commonly called a testbench.

Verilog HDL language can be used for RTL (register transfer level) circuit design with a high degree of abstraction. RTL is a design model that describes circuit actions according to signal flow between registers and circuit logic. One can design hardware in a Verilog HDL IDE (for FPGA implementation such as Xilinx ISE, or Altera Quartus) to produce the RTL schematic of the desired circuit. After that, the generated schematic can be verified using simulation software which shows the waveforms of inputs and outputs of

the circuit after generating the appropriate testbench. To generate an appropriate testbench for a particular circuit or Verilog HDL code, the inputs have to be defined correctly. For example, for clock input, a loop process or an iterative statement is required.

The key advantage of Verilog HDL when used for systems design is that it allows the behaviour of the required system to be described (modelled) and verified (simulated) before synthesis tools translate the design into real hardware (gates and wires).

Another benefit is that Verilog HDL allows the description of a concurrent system (many parts, each with its sub-behaviour, working together at the same time). Verilog HDL is a Dataflow language, unlike procedural computing languages such as BASIC, C, and assembly code, which all run sequentially, one instruction at a time.

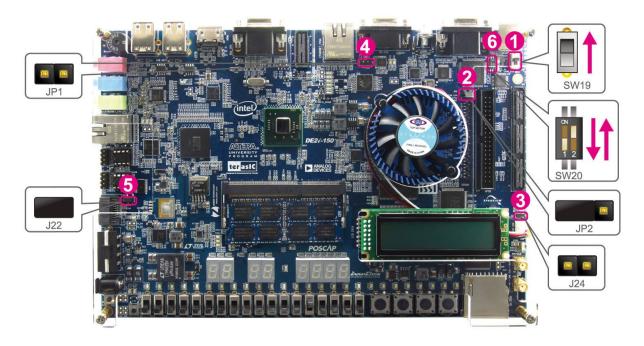

### 1.5 DE2i-150 FPGA Board

FPGA stands for field-programmable gate array. At its core, an FPGA is an array of interconnected digital subcircuits that implement common functions while also offering very high levels of flexibility. Where the user can program what the logic gate does (be it a NAND or NOR or some form of SUM-of-PRODUCT implementation) or an adder, you as a user, can "program" the chip to perform that logic function. Now we can add another layer of user programmability – you can program how these logic gates are connected! In that way, we have a general programmable logic chip. Unlike the microprocessor where the program is just the instruction to fix digital hardware, here you can program the hardware itself!

The first FPGA was introduced by Xilinx in 1985. It has arrays of logic blocks that are programmable. It is surrounded by PROGRAMMABLE ROUTING RESOURCES, which allows the user to define the interconnections between the logic blocks. It also has lots of very flexible input and output circuits that

programmable for TTL (Transistor-Transistor Logic), CMOS (Complementary Metal Oxide Semiconductor), and other interface standards.

Nowadays, there are two major players in the FPGA domain: Xilinx and Altera (now part of Intel). These two companies dominate 90% of the FPGA market with roughly equal shares.

Figure 4. The DE2i-150 board (top view)

At this point when a Verilog HDL model completed here, we translate it into "gates and wires" that are mapped onto the programmable logic device such as a DE2i-150 FPGA, then it is the actual hardware being configured, rather than the Verilog HDL code being "executed" as if on some form of the processor chip.

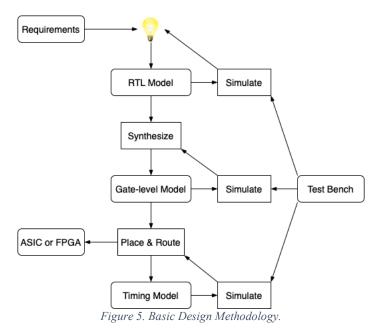

## Chapter 2: Design Methodology

A Pipelined Processor Design is referred to as a Pipelined CPU. The CPU is a device that executes various software instructions and data processing. In designing a CPU, we must first define its instruction set and how many instructions do we want? What are the instructions? What opcode do we assign to each of the instructions? How many bits do we use to encode an instruction? Once we have decided on the instruction set, we can proceed to design an architecture that can execute all the instructions in the instruction set. In this step we are creating a custom structure, so we need to answer questions such as How many registers do we need? Do we use a single register file separate register? How the different units are connected? Finally, we can design the control unit. Just like the dedicated processor, the control unit asserts the control signals to the processor. This finite state machine cycles through two main states: 1) idle; 2) execute. The control unit performs these states by sending the appropriate control signals to the processing. And the processor consists of general-purpose registers and various special-purpose registers such as PC (Program counter).

The five-stage design of the processor is similar to the MIPS architecture, it is designed according to the pipeline structure. As long as the CPU obtains data from the memory, the execution of each MIPS instruction is divided into five flowing stages, and each stage takes up a fixed time, usually only one processor clock cycle.

Figure 6. Single-Cycle CPU logic architecture

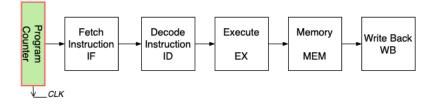

When the processor is designed, the execution phase of the processor is divided into the following five stages:

- 1. IF: Instruction Fetch. Get the next instruction from the instruction memory

- 2. ID: Instruction Decode (Read Register). Translate instructions, identify opcodes and operands, and read data from the register heap to the ALU input register.

- 3. EX (ALU): Execute, (arithmetic/logical operation). Complete arithmetic or logical operations in a clock cycle. Note that floating-point arithmetic and integer multiplication and division operations cannot be completed in a single clock cycle which we didn't use in our design.

- 4. MEM: Memory Access, memory data read or write. At this stage, instructions can read/write memory variables from data memory. On average, about three-quarters of instruction do not perform any operations at this stage. This stage is assigned to each instruction to ensure that no two instructions will access the data cache at the same time.

- 5. WB: Write Back. After the operation is completed, write the calculation results from the ALU output register back to the general register.

## 2.1 Datapath

The Datapath is responsible for the manipulation of data. It includes ALU, registers, memory elements for the temporary storage of data, buses, and multiplexers for the transfer of data between the different components in the Datapath. External data can be entered into the Datapath through the data input lines. Results from the computation are provided through the Datapath output lines.

For the Datapath to function correctly, appropriate control signals must be asserted at the right time. Control signals are needed for all the select and control lines for all the components used in the Datapath. This includes all the select lines for multiplexers, ALU, and other functional units having multiple operations, all the read/write enable signals for registers and register files, address lines for register files, and enable signals for tri-state buffers. The operation of the Datapath is determined by which control signals are asserted and at what time. In a processor, these control signals are generated by the control unit. In return, the Datapath needs to supply status signals back to the control unit for it to operate correctly. These status signals provide input information for the control unit to determine what operation to perform next. Since the Datapath must be able to perform all the operations required to solve the given problem. For example, if the problem requires the addition of two numbers, the Datapath, therefore, must contain an Adder. If the problem requires the storage of three temporary variables, the Datapath must have three registers.

However, even with these requirements, there are still many options as to what is implemented in the Datapath. Registers can be separate register units or combined in a register file. Furthermore, two temporary variables can share the same register if they are not needed at the same time. Datapath design is also referred to as the **register-transfer level (RTL)** design. In the register-transfer level design, we look at how data is transferred from one register to another or back to the same register. If the same data is written back to a register, the data passes through one or more functional units and gets modified. The time from the reading of the data to the modifying of the data by functional units and finally to the writing of the data back to a register must all happen within one clock cycle.

The Top-view of the design should look as follows, in which select\_out selects the output signal is related to the CPU board-level test by using 7-segment light.

Figure 7. CPU top view

According to the Top view, the entire Processor is divided into 6 modules:

- 1. **Processor** main module: perform arithmetic processing with the instructions obtained from the instruction memory, and write or read data from the data memory. This is the core part.

- 2. **Instruction Memory** instruction module: Provide instructions for the Processor module, so that the Processor can find the memory address of the instruction through the value in the instruction register, thereby reading the instruction.

- 3. Data Memory data module: Processor reads data or writes data.

- 4. Clock Generator: is an electronic oscillator that produces a clock signal for use in synchronizing a circuit's operation.

- 5. **Processor Controller**: It is used to control the processor execution by the clock

- 6. **7-Segment Interface**: a seven-segment display is a form of an electronic display device for displaying decimal numerals that are an alternative to the more complex dot matrix displays.

## **2.2**The Instruction Set Architecture